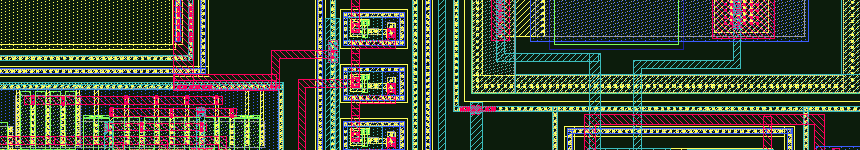

65/55nm Optimized Memory IP

Mobile Semiconductor’s silicon-proven embedded SRAM technology offers optimized memory solutions for both TSMC and SMIC 65nm low-power processes. These memory compilers are available in a range of architectures:

low voltage, low leakage, low power SRAM (LV)

via programmable low voltage, low power ROM (LV)

high speed SRAM (HS)

high density SRAM (HD)

Mobile Semiconductor’s proprietary design and layout techniques are applied to all architectures to optimize performance while keeping die size small.

Single-port low voltage (LV) SRAM memories use high VT devices and source biasing to minimize standby currents with limited standard VT devices used when required. This architecture provides a low power SRAM with low dynamic power, minimal peak current, and also includes a retention mode for ultra low leakage standby SRAM.

Single-port low power ROM instances use high VT devices with limited standard VT devices used when required. The sub-divided bit line architecture results in low peak currents and low dynamic power. The ROM content is programmable in the via1 layer.

Single-port high speed (HS) memories use low VT and standard VT devices to optimize the critical path and enhance performance while limiting static current.

Single-port high density (HD) memories use standard VT devices to optimize the critical path and enhance performance.

TSMC 65nm LP

Mobile Semiconductor offers an optimized TSMC 65nm LP-process single-port low voltage (LV) embedded low power SRAM and ROM compilers.

To ensure high manufacturing yield, the Trailblaze™ software utilizes TSMC’s standard high density 6T bit cells and is consistent with TSMC’s Design for Manufacturing (DFM) guidelines for the 65nm LP process.

Mobile Semiconductor Optimized TSMC 65nm LP Architecture

Single-Port Low Voltage SRAM

Low Voltage Via Programmable ROM

TSMC 55nm LP

Mobile Semiconductor offers an optimized TSMC 65nm LP-process single-port low voltage (LV) embedded SRAM solution.

To ensure high manufacturing yield, the Trailblaze™ software utilizes TSMC’s standard high density 6T bit cells and is consistent with TSMC’s Design for Manufacturing (DFM) guidelines for the 65nm LP process.

Mobile Semiconductor Optimized TSMC 55nm LP Architecture

Single-Port Low Voltage SRAM

Single-Port LV SRAM (Flash process)

Global Foundries 55nm LPE

Mobile Semiconductor offers an optimized Global Foundries 55nm LPE-process single-port low voltage (LV) embedded SRAM and ROM solutions.

To ensure high manufacturing yield, the Trailblaze™ software utilizes Global Foundries’s standard high density 6T bit cells and is consistent with Global Foundries’s Design for Manufacturing (DFM) guidelines for the 55nm LP process.

Mobile Semiconductor Optimized Global Foundries 55nm LP Architecture

Single-Port Low Voltage SRAM

Single-Port LV SRAM (Flash process)

Low Voltage Via Programmable ROM

SMIC 65nm LL

Mobile Semiconductor’s optimized SMIC 65nm LL-process embedded single-port SRAM solutions are offered in high speed (HS) and high density (HD) architectures.

In order to ensure high manufacturing yield, the Trailblaze™ software utilizes SMIC’s standard high density 6T bit cells and is consistent with SMIC’s Design for Manufacturing (DFM) guidelines for the 65nm LL process.

Mobile Semiconductor Optimized SMIC 65nm LL Architecture

Single-Port, High Speed SRAM

Single-Port, High Density SRAM

Trailblaze™ Compiler Name

Custom Solutions

Don’t see what you’re looking for? Let Mobile Semiconductor’s highest level of industry expertise bring you the optimized, embedded SRAM solution you need to quickly bring your next product to market. Find out how…